18. CPU-instruction Cycle step by step

19 May 2020 | CS

CPU-instruction Cycle step by step

-

the CPU is executes only one part of instruction at a time but CPU can perform all lightening speed and it can execute millions of such part instructions in just one second.

-

therefore, this high speed of execution creates an illusion that all program are running simultaneously on the system, but that is not the case.

-

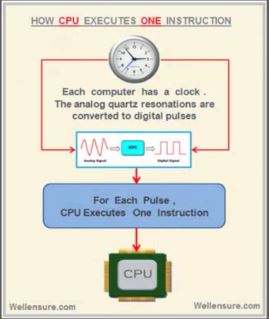

A CPU is driven by an internal clock that regulates the rate at which instruction are executed by the CPU and synchronizes all other components part of the computer system.

-

Every microprocessor requires a clock(binary square pulse) for its functioning. the CPU requires a fixed number of clock ticks (called as clock sycle/ clock speed) to execute each instruction.

-

the faster the clock cycle, the CPU can execute more part instructions per seconds. And therefore the number of clock cycles per second is known as processor speed. the processor speed is expressed in MHz Or GHz.

-

clocking is required to time and synchronize the various circuits.

-

the number of clock cycles per second is known as frequecny

- Each CPU contains high speed memory areas registers and Level1 cache memory to store data and instruction during the various stages of execution of the instruction cycle. the CPU can directly access the registers to perform operation on the data.

-

the CPU first loads the PC(Program Counter) register with the address of the first instruction to be executed.

-

this address in the PC register is then transferred to the MAR(memory address register) and the CPU simultaneously increments the PC register by 1 so that now it contains the address of the next instructions.

-

the contents of the MAR are placed on the address bus

-

the control unit of the CPU sends two clock pulses on the control lines and this has individual effects (a) the low pulse on the CS line switches on the chip. (b) the low pulse on the R/W line reads or writes the conetens at the given memory address.

-

As a result of the two low clock pulse causes the instruction or data is taken on the data bus to MBR(memory buffer register). this fetched instruction is then placed in the CIR(IR) current instruction register. at this stage the “fetch” part of instruction cycle ends and “Decode” part starts.

-

the CIR(current instruction Register) breaks down the instruction in two parts(Opcode and Operand). the Opcode is sent to the instruction decoder where the operation to be performed by the ALU is decided based on the instruction set of the processor. the operand may either contain data or address as specified in the addressing mode in the Opcode. At this stage the “decode” part of the instruction cycle ends and “Execution” part starts.

-

the instruction after being decoded is sent to execution unit ALU(Arithmetic Logic Unit) of the CPU. this is the last part of the instruction cycle where “execution” part starts. the ALU perform the operation on the data as specified in the program instruction. the result of this operation is temporarily stored in another register called “Accumulator” which is placed inside the ALU. the result is then transferred to either output device, storage or displayed.

CPU-instruction Cycle step by step

-

the CPU is executes only one part of instruction at a time but CPU can perform all lightening speed and it can execute millions of such part instructions in just one second.

-

therefore, this high speed of execution creates an illusion that all program are running simultaneously on the system, but that is not the case.

-

A CPU is driven by an internal clock that regulates the rate at which instruction are executed by the CPU and synchronizes all other components part of the computer system.

-

Every microprocessor requires a clock(binary square pulse) for its functioning. the CPU requires a fixed number of clock ticks (called as clock sycle/ clock speed) to execute each instruction.

-

the faster the clock cycle, the CPU can execute more part instructions per seconds. And therefore the number of clock cycles per second is known as processor speed. the processor speed is expressed in MHz Or GHz.

-

clocking is required to time and synchronize the various circuits.

-

the number of clock cycles per second is known as frequecny

- Each CPU contains high speed memory areas registers and Level1 cache memory to store data and instruction during the various stages of execution of the instruction cycle. the CPU can directly access the registers to perform operation on the data.

-

the CPU first loads the PC(Program Counter) register with the address of the first instruction to be executed.

-

this address in the PC register is then transferred to the MAR(memory address register) and the CPU simultaneously increments the PC register by 1 so that now it contains the address of the next instructions.

-

the contents of the MAR are placed on the address bus

-

the control unit of the CPU sends two clock pulses on the control lines and this has individual effects (a) the low pulse on the CS line switches on the chip. (b) the low pulse on the R/W line reads or writes the conetens at the given memory address.

-

As a result of the two low clock pulse causes the instruction or data is taken on the data bus to MBR(memory buffer register). this fetched instruction is then placed in the CIR(IR) current instruction register. at this stage the “fetch” part of instruction cycle ends and “Decode” part starts.

-

the CIR(current instruction Register) breaks down the instruction in two parts(Opcode and Operand). the Opcode is sent to the instruction decoder where the operation to be performed by the ALU is decided based on the instruction set of the processor. the operand may either contain data or address as specified in the addressing mode in the Opcode. At this stage the “decode” part of the instruction cycle ends and “Execution” part starts.

-

the instruction after being decoded is sent to execution unit ALU(Arithmetic Logic Unit) of the CPU. this is the last part of the instruction cycle where “execution” part starts. the ALU perform the operation on the data as specified in the program instruction. the result of this operation is temporarily stored in another register called “Accumulator” which is placed inside the ALU. the result is then transferred to either output device, storage or displayed.

Comments